发布日期:2024-11-08 浏览次数:

供稿:凝聚态物理与材料物理研究所 |

编校:时畅 |

编辑:陈伟华 |

审核:杨学林

近日,太阳成集团tyc234cc凝聚态物理与材料物理研究所、纳光电子前沿科学中心、人工微结构和介观物理国家重点实验室叶堉课题组与合作者提出了一种共溅射掺杂技术,在二维半导体碲化钼薄膜中实现精准地空穴导电(p型)或电子导电(n型)的二维半导体掺杂技术。此外,共溅射掺杂技术可在碲化钼薄膜中进行空间区域的选择性掺杂,将p型和n型的碲化钼薄膜集成在单一基底上。利用上述技术,成功制造出芯片尺寸的二维互补型反相器电路阵列,该电路具有出色的器件性能和良率,展示了二维半导体材料在大规模集成电路中的应用潜力。2024年11月7日,相关研究成果以“用于单片集成电路的二维半导体精准p型和n型掺杂技术”(Precisep-type andn-type doping of two-dimensional semiconductors for monolithic integrated circuits)为题发表于《自然·通讯》(Nature Communications)上。

掺杂技术是现代集成电路产业的基础,是指在半导体材料中人工掺入一定量的特定杂质原子,以改变半导体材料的电学性能,由此可以制造出各种功能型电子器件和电路。例如半导体硅,可以在熔融过程之前添加诸如磷或硼之类的掺杂剂,随后通过提拉法生产具有不同导电性类型和导电能力的掺杂单晶硅晶圆片。此外,离子注入是硅基集成电路的一项基本技术,可以选择性掺杂特定区域以构筑p型区和n型区,进而制造互补型集成电路芯片。二维原子晶体,由于其原子厚度和堆叠能力,已经成为推进摩尔定律的候选材料之一,特别是在晶体管缩放和层间互连方面。然而,上述掺杂技术在二维半导体材料中进展缓慢,主要原因是很难在合成过程中精准微量的进行杂质原子掺入,并且像离子注入这样的传统工艺对原子级厚度的二维原子晶体无法实现有效的空间选择性掺杂。

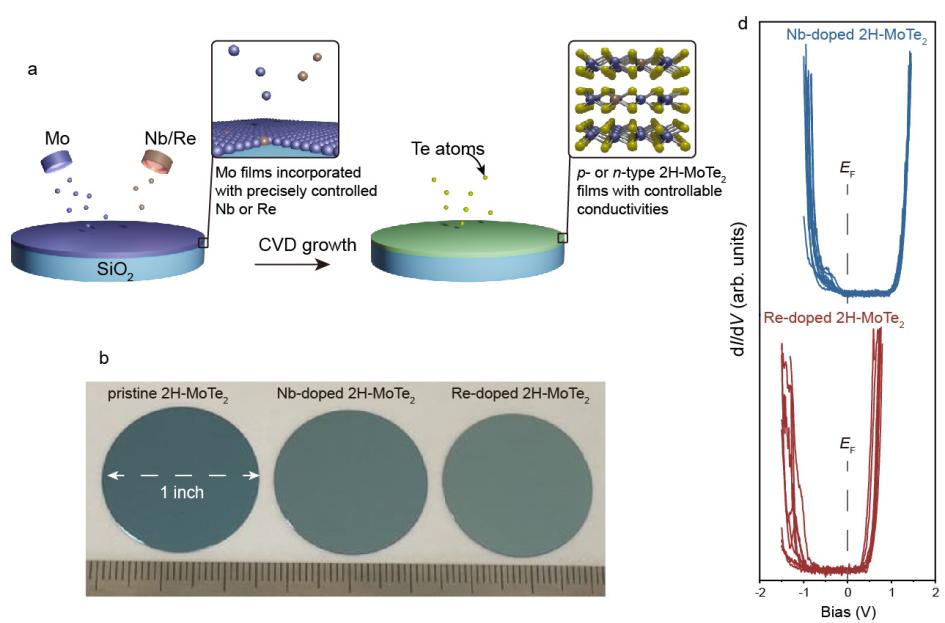

基于上述研究背景,叶堉课题组与合作者在前期二维碲化钼薄膜相变与可控制备的基础上,提出二维半导体碲化钼(MoTe2)薄膜的共溅射掺杂技术。利用双靶位共溅射方式,在高温碲化之前向钼膜中精准控制掺入一定量的杂质元素铌(用于空穴掺杂)或铼(用于电子掺杂)。然后,通过化学气相沉积(CVD)碲化Mo膜前驱体从而获得掺杂的少层MoTe2膜(图1 a)。利用该方法可以制备大面积、晶圆尺寸的掺杂二维半导体MoTe2薄膜(图1 b),展示其大规模应用的潜力。与此同时,对掺杂后的二维MoTe2薄膜进行扫描隧道显微镜微分电导谱(STS)表征(图1 c)。通过STS表征结果可清晰观察到MoTe2半导体随着掺杂元素的改变,其费米能级(EF)位置明显移动。对于铌(Nb)掺杂的情况,EF更接近价带顶,表现出p型半导体特征。而铼(Re)元素的掺杂结果则相反,其费米能级更靠近导带底。考虑到样品之间的唯一区别是在Mo膜前驱体中引入了不同的杂质原子,并且它们是在相同的条件下制备和测量的,因此可以排除分子吸附或环境因素对费米能级位置的影响。STS的表征结果直观地展现出掺杂剂对二维半导体MoTe2的费米能级位置的影响,随后研究人员对掺杂的MoTe2半导体进行电学特性的表征分析。

图1.利用共溅射掺杂技术制备晶圆级掺杂二维碲化钼薄膜,并用扫描隧道显微镜谱对其半导体能带结构进行表征分析。

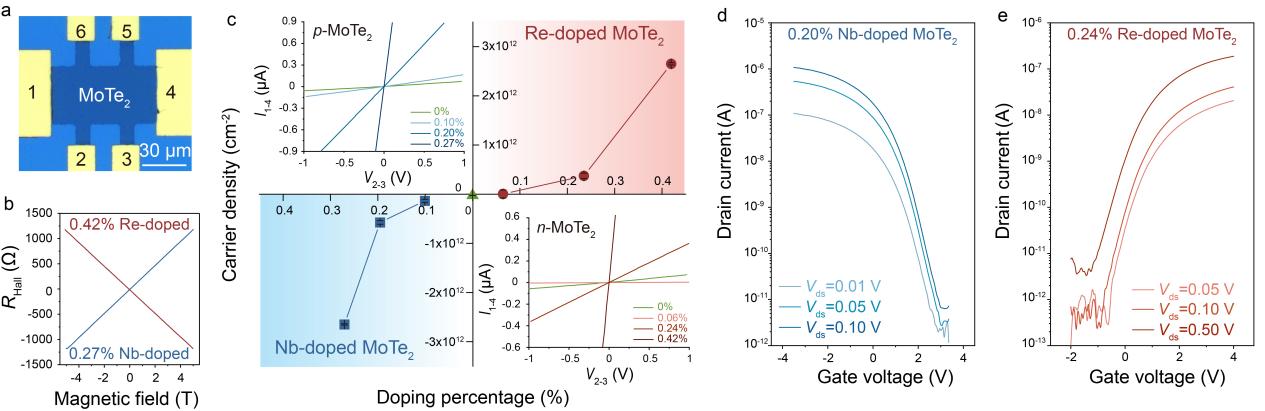

在确定Nb和Re掺杂剂对二维半导体MoTe2的有效p型和n型掺杂后,必须考虑的是实现可控的精准掺杂,特别是掺杂过程中产生的载流子浓度的表征。为了控制Mo薄膜中掺杂的比例,合作团队在共溅射过程中保持Mo的沉积速率恒定的情况下,同时对掺杂剂(Nb或Re)的沉积速率进行微调,实现了微量掺杂Nb(0.10%)和Re(0.06%)。随后,通过CVD生长获得了不同载流子类型和载流子浓度的MoTe2薄膜。为不同的样品制作霍尔器件以表征其载流子类型和浓度(图2 a)。Nb和Re掺杂样品的霍尔电阻测量显示出相反的极性,进一步证实了Nb(Re)掺杂分别在MoTe2薄膜中引入了空穴(电子)载流子。通过计算霍尔电阻随磁场变化曲线斜率的倒数来确定载流子浓度。未人工掺杂的MoTe2显示出较低的空穴载流子浓度(2.66×1010cm−2)。在加入微量掺杂剂Re(0.06%)后,对空穴载流子进行补偿,将样品转化为电子浓度为3.94×109cm−2的导电材料。之后,进一步提高杂质靶材的溅射功率,电子浓度随Re掺杂量的增加而增加。同样,随着Nb掺杂量的增加,样品中的空穴浓度也随之增加。随着p型和n型杂质载流子浓度的增加,掺杂MoTe2薄膜的电导率逐渐增加,这可以从四探针电流-电压曲线中得到证明(图2 c的插图)。对适当掺杂浓度的MoTe2薄膜进行场效应晶体管器件制备和电学测试,器件的转移特性曲线可观察到明显的p型和n型沟道特征,开关比约为105。成功制备的可控制掺杂类型和载流子浓度的二维半导体MoTe2薄膜,具有实际的电子器件应用潜力。

图2.对掺杂的二维半导体碲化钼薄膜进行霍尔电学表征和晶体管性能测试。

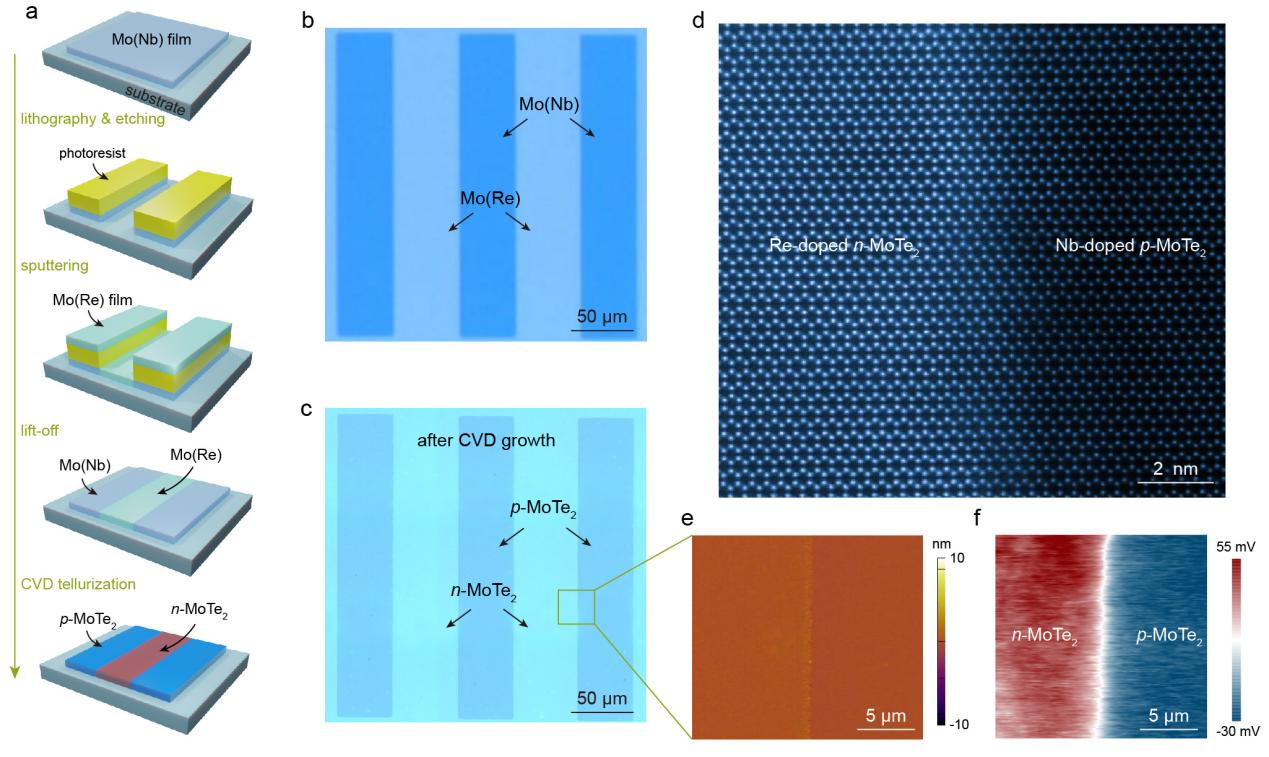

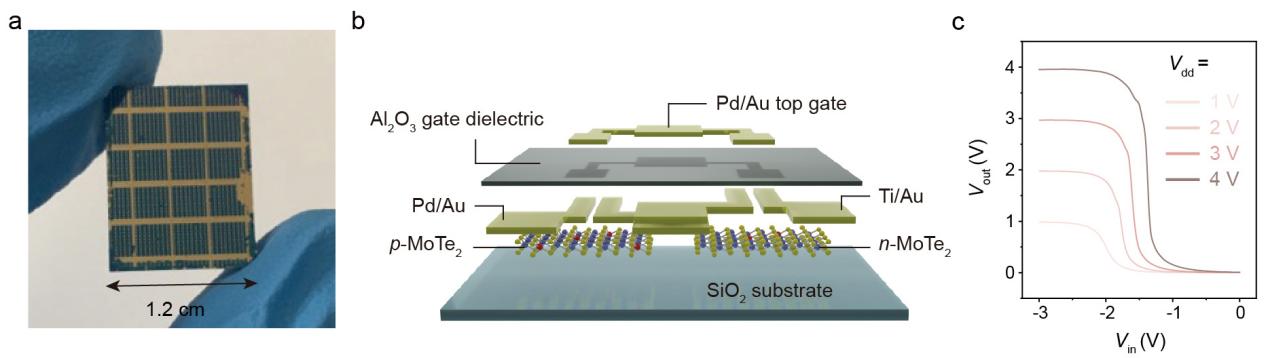

对半导体材料空间区域选择性掺杂是实现集成电路的关键步骤。基于已开发的共溅射掺杂技术和MoTe2薄膜“固-固”相变过程,我们设计了一步生长方法来获得二维半导体MoTe2薄膜的图案化掺杂结构。首先,在衬底上沉积Nb掺杂的Mo膜,然后使用传统的光刻和物理蚀刻技术进行图案化(图3 a)。随后,沉积Re掺杂的Mo膜,在去胶过程之后,获得包含Nb和Re掺杂区域的连续图案化前驱体Mo膜(图3 b)。采用一步CVD生长方法合成了平面集成的p型和n型图案化MoTe2薄膜(图3 c)。在相变和再结晶过程中,单晶MoTe2晶畴延伸到不同掺杂区域的界面上,形成了具有p型和n型图案化区域的单晶MoTe2薄膜。高角度环形暗场扫描透射电子显微镜(HAADF-STEM)图像显示Nb掺杂和Re掺杂区域之间的界面有一个完美的晶格,没有任何晶向角度偏转和晶界(图3 d)。利用开尔文探针原子力显微镜(KPFM)测量界面表面电势差,验证了掺杂诱导费米能级位移的有效性。与Nb掺杂的MoTe2相比,Re掺杂的MoTe2区域表现出明显更高的表面电势(图3 f),符合预期的掺杂特性。利用空间区域的选择性掺杂技术,合作团队制备了大面积p-MoTe2和n-MoTe2单片集成的二维材料反相器电路阵列(图4 a和b)。当驱动电压Vdd=4 V时,反相器电路增益达到38,功耗89 nW。综上所述,研究人员提出一种有效、可控的二维半导体精准掺杂技术,有利于促进二维半导体材料在单片集成互补型电路领域中的应用。

图3.对二维半导体碲化钼薄膜进行共溅射空间区域选择性掺杂及其扫描透射电子显微镜(STEM)和开尔文探针原子力显微镜(KPFM)表征分析。

图4.大面积制备基于二维掺杂碲化钼半导体的互补型反相器电路阵列及其性能测试。

太阳成集团tyc234cc博雅博士后潘宇为该工作第一作者;武汉大学何军教授和张晨栋教授、北京理工大学徐晓龙预聘教授、太阳成集团tyc234cc叶堉研究员为共同通讯作者,主要合作者还包括太阳成集团tyc234cc高鹏教授。

上述研究工作得到国家重点研发计划、国家自然科学基金、北京市自然科学基金、太阳成集团tyc234cc长三角光电科学,以及人工微结构和介观物理国家重点实验室等支持。

论文原文链接:https://www.nature.com/articles/s41467-024-54050-2.pdf